模型晶振(PCB 晶振怎么设计?工作原理+设计步骤详解,手把手教你设计,秒懂)

Posted

篇首语:时穷节乃现,一一垂丹青。本文由小常识网(cha138.com)小编为大家整理,主要介绍了模型晶振(PCB 晶振怎么设计?工作原理+设计步骤详解,手把手教你设计,秒懂)相关的知识,希望对你有一定的参考价值。

模型晶振(PCB 晶振怎么设计?工作原理+设计步骤详解,手把手教你设计,秒懂)

大家好,我是百芯,可以叫我老百姓(老百芯)[笑哭]

之后我会在这里和大家分享 DFM可制造性分析、PCB设计、DFM工具,电路设计等相关的知识,请大家多多指教。

今天主要给大家简单介绍一下:PCB 上晶体振荡电路的设计。

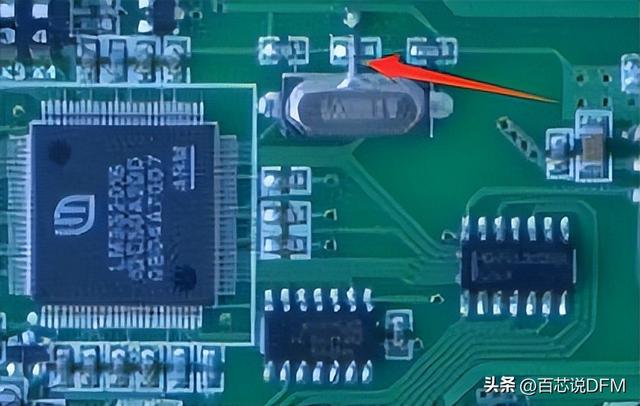

晶振实物图

在大部分电路中,设计晶体振荡电路是经常会遇到的。网络上也有很多关于晶体振荡器设计的笔记,不过都是针对大规模生产,这种方法也需要投入大量的测试和不断地进行优化。

这篇文章更加适合小型的电路项目,可以帮助你设计晶体振荡器和选择合适的负载电容。

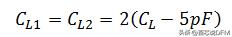

PCB 图

一、PCB上 晶体振荡电路设计步骤

这里主要有 4个简单的步骤:

1、选择晶体振荡器

选择晶体振荡器需要考虑到以下3 个因素:

- 可拉性与功耗

- 振荡器对频率变化的功耗启动时间与封装尺寸

- 上电后达到稳定振荡所需要的时间成本

1) 可拉性与功耗

一般来说,拉力低的晶体振荡器需要较大的负载。每个振荡周期都必须要释放电容的能力,因此更大的负载电容意味着更高的功耗损耗。

很多微控制器的 datasheet 中都会有推荐负载电容的最大值,这样的话可以减低驱动电路中的功耗。

2) 振荡器对频率变化的功耗启动时间与封装尺寸

较小的晶体振荡器封装具有较大的 ESR ,较大的 ESR 会提供较大的临界增益(gm_crit),从而降低增益宽=裕度。

增益裕度降低意味着晶体需要更长的时间才能启动。

3) 上电后达到稳定振荡所需要的时间成本

其实很多时候性能和成本并不是强关联,如果在满足性能下,可以选择成本相对较低的晶体振荡器。

2、检查微控制器是否可以驱动晶体振荡器

通常来微控制器的 datasheet 中会提供一些关于怎么选择晶体振荡器。这些参数与临界增益由关,临界增益是微控制器电路启动晶体振荡器所需的最小增益。

有的 datasheet 还会提供一组给定频率和负载电容的晶体振荡器允许的最大的 ESR。

如果微控制器数据表提供振荡器跨导(通常以uA/V为单位)或最大临界增益,那么我们需要计算晶体的临界增益并检查微控制器是否可以驱动它。

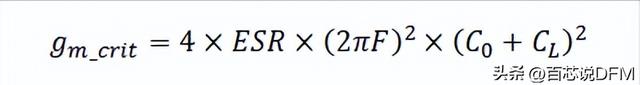

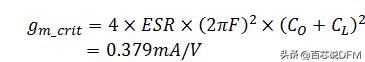

下面为临界增益计算公式:

临界增益公式

在这个公式中:

- F 是晶体振荡器的标称频率

- ESR 是晶体的等效串联电阻

- CO 是晶振并联电容

- CL 是晶体的标称负载电容

临界增益是晶体的一个属性,这些参数在晶体的数据手册中。

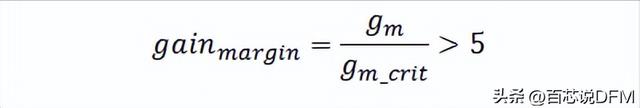

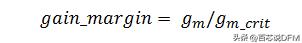

接下来计算增益裕度。如果增益余量大于5,则振荡器将可靠启动。更大的增益余量意味着更快的振荡器启动。

晶体振荡器的启动条件:增益余量大于5,如下公式所示:

晶体振荡器的启动条件

下面为增益裕度计算公式:

增益裕度

或者,一些微控制器数据表提供了最大临界增益gm_crit_max。在这种情况下,gm_crit必须小于gm_crit_max。

如果微控制器不满足驱动晶振的要求,就需要重新选择晶体振荡器。

3、晶体振荡器的功耗

datasheet 中会指定了晶体的驱动电平 (DL),驱动电平基本上是晶振正常工作时的最大额定功率。

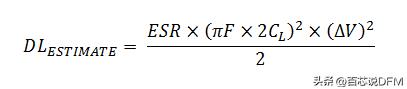

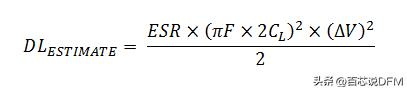

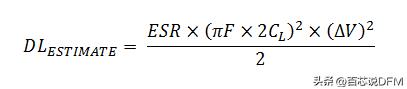

驱动电平的粗略估计可以用下面这个公式计算:

驱动电平驱动电平计算公式

在上面这个公式中:

- △V 是峰峰值振荡器电压——最坏的情况:△V=Vcc

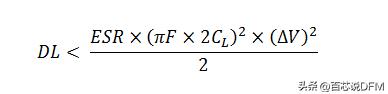

如果估计值低于晶体振荡器的额定驱动电平,则直接进行下一步。

符合要求的驱动电平

如果估计值高于晶体振荡器的额定驱动电平,你可以改进估计值或者重新另外的晶体振荡器。

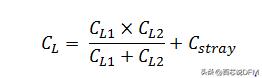

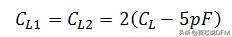

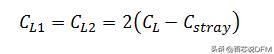

4、选择负载电容 CL1和 CL2

第一次设计晶体振荡电路的时候,先假设两个负责电容是并联的。选择了CL1=CL2=0.5*CL,但经过验证过后,这是错误的。

负载电容是晶体两端所需的电容,因此 CL1 和CL2 串联。负载电容的计算公式如下所示:

负载电容的计算公式

将负载电容的计算公式简化一下,简化后的公式如下所示:

简化后的负载电容计算公式

Cstray 是来自微控制器引脚和走线电容的杂散电容的累积,很多有经验的工程师建议,将这个值估计为 5pF 左右。

则公式为以下:

负载电容公式

一些微控制器数据手册提供了更准确数据一一例如,msp430f22x2系列指定了 1pF 的杂散电容,非常适合其低功耗模型。

二、PCB 中晶体振荡电路设计

这里希望通过 PCB 布局来最小化振荡器和外部信号之间的耦合,因为高频耦合会激发晶体振荡器的高次谐波,晶振是干扰外部电路的噪声源。

具体有以下几点需要注意:

1、晶体振荡器靠近微控制器

短走线具有低互感和电容,长走线具有高互感和电容。使晶体靠近微控制器可以缩短走线,从而减少耦合。所以走线的长度尽可能短,但不能与其他信号线交叉。

2、振荡器电路与高频电路隔离开

路由非振荡器信号时,高频电路要远离振荡器电路。也可以考虑使用带有通孔的铜迹线,围绕着振荡器电路,这将减少外部信号线和振荡器之间的互感。

振荡器电路与高频电路隔离开

通常的做法是将振荡器电路下方的接地层分开,仅在一点点连接分离的接地层,就在微控制器接地旁边。这可以防止来自其他信号源的返回电流通过振荡器使用的接地层。上图的示例就是按照这种方法,只是没有很明显。

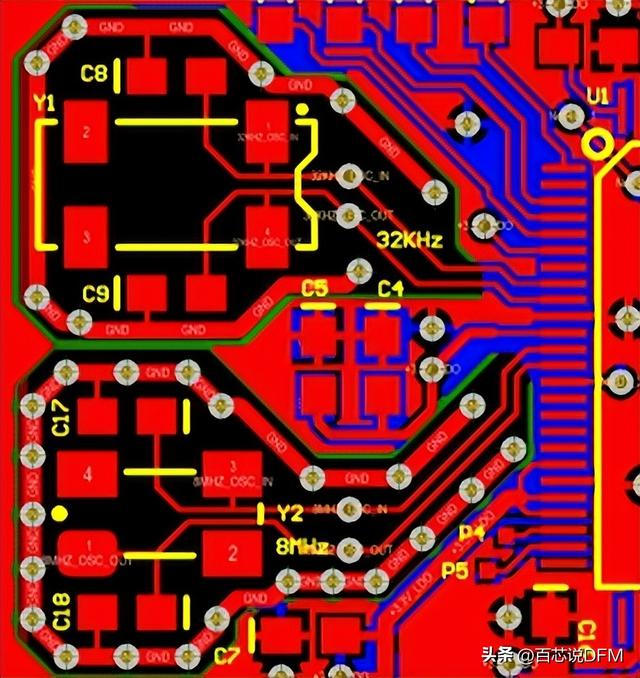

3、晶振靠近 CPU 芯片摆放,但要尽量远离板边。

因为内部石英晶体的存在,由于外部冲击或跌落容易损坏石英晶体,从而造成晶体不振荡,在设计可靠的安装电路时要考虑晶体,靠近 CPU 芯片的位置优先放置远离板块的一面。

晶振放置图

(圆柱晶振)外壳接地后,加一个与晶振形状相似的长方形焊盘,让晶振“平放”在这个焊盘上,并在焊盘的两个长边附近开一个孔(孔要落在焊盘上,最好用多层焊盘代替孔,两个多层焊盘要接矩形焊盘),然后用铜线或其他裸线将晶振“箍”起来,铜线的两端焊接在你开的两个孔或焊盘上。这样可以避免高温焊接对晶振的损坏,保证良好的接地。

4、手工或机器焊接时,要注意焊接温度

晶振对温度敏感,焊接时温度不宜过高,加热时间尽量短。

焊接图片

5、耦合电容应尽量靠近晶振的电源管脚放置

放置顺序:根据功率流向,按电容值从小到大排列,电容最小的电容值最接近电源引脚。

6、晶振外壳接地

晶振外壳接地(如果接地影响负载电容的话,就不能接地),既可以从晶振向外辐射,也可以屏蔽外界信号对晶振的干扰。

7、不要在晶振下方布线,确保完全铺设好地线

在晶振 300mil 范围内不要布线,以免晶振干扰其他布线、器件和层的性能。

8、时钟信号的走线尽量短,线宽要大一些

时钟信号的走线尽量短,线宽要大一些。在布线长度与热源的距离之间找到平衡点。

三、示例1∶为 STM32 设计 8MHZ 晶体振荡器

STM32实物图

1、选择晶振

STM32F427 数据手册中要求:

- 对于 4-26MHz 晶体,Gm_crit_max=1mA/V

- 频率容差必须为 +/-500ppm 或更好

- CL1 和 CL2 建议在 5pF 到 25pF 之间

这里我们选择 7A-8.000MAAJ-T,虽然 STM32 的引脚间距为0.5mm,但晶振的尺寸小,可以放置在靠近在 STM32的位置。

7A-8.000MAAJ-T 晶振的特性:

- CL= 18 pF

- ESR= 60 Ω

- 频率稳定性= 50 ppm

- 频率容差= 30 ppm

- CO= 7pFmax

- 驱动电平(DL)= 500uW max

2、检查微控制器是否可以驱动晶振,计算 gm_crit(增益裕度)∶

gm_crit计算公式

所以gm_crit低于Gm_critmax,振荡器电路将可靠启动。

3、晶振可以处理功率损耗吗?

这里粗略估计电路的驱动电平∶

驱动电平计算公式

计算得 DL =267uW,低于晶体允许的最大驱动电平500uW。

4、选择 负载电容 CL1 和 CL2

假设 Cstray=5pF,则∶

负载电容公式

CL1=26pF

STM32 建议将 CL1和CL2保持在 25pF 以下,所以可以选 24 pF 的电容。

四、示例2∶为 ATMEGA328 选择 16MHZ 晶体振荡器

ATMEGA328

1、选择晶振

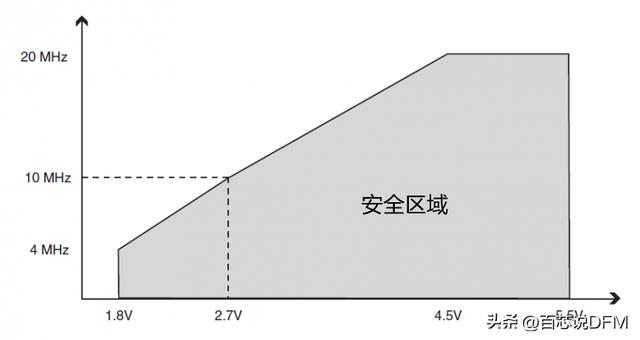

ATMega328 数据手册的要求:

- 16MHz 的最小电压为 3.78V,以适应安全操作,如图下所示。要驱动 16MHz 时钟,我们必须在 3.78V 或以上,对于本设计,我们在 5V 下工作。

- CL1 和 CL2 建议在 12pF 到 22pF 之间

ATMega328 数据手册

这里选择 9B-16.000MAAE-B 晶振。9B-16.000MAAE-B 晶振 的特性参数如下所示:

- CL= 12pF

- ESR = 30Ω

- 频率稳定性= 30ppm

- 频率容差= 30ppm

- C0= 7pFmax

- 驱动电平( DL)=500uWmax

2、检查微控制器是否可以驱动晶振

ATMega328 的数据表中没有跨导规范,这里就必须让开发人员设置好保险丝,以便在填充 PCB 后启用振荡器。

3、晶振可以处理功率损耗吗?

粗略估计电路的驱动电平(DL)∶

驱动电平计算

驱动电平( DL )=545uW。

驱动电平估计值太高。但是,如果选择 CL1并且表明设计的功耗是可以承受的,就可以改进这个估计值。

4、选择 负载电容 CL1 和 CL2

假设Cstray=5pF,则∶

负载电容 计算

CL1= 14PF。

参考来源:https://hoani.net/posts/blog

以上就是关于 PCB 晶振电路的设计与布局,希望大家多多支持。

图片来源于网络

记得点赞、分享、收藏、转发,评论。

相关参考

1、晶振的简介晶振,也称为振荡器。英文名为oscillator,通常有四个管脚和方向,它有功率、质量和时钟输出引脚,里面有晶体和振荡电路。无需输入信号源,可直接生成频率,频率在出厂时校准。特点:使用方便,频率稳定...

石英晶振的核心功能是高精度频率源,被广泛应用于无线数据传输与计时,常被誉为电子产品的“心脏”,但如果按晶振的功能和实现技术分类,可以分为哪几种?晶振-星光鸿创普通晶振普通晶体振荡器是最简单的晶体振荡器,...

在单片机的学习中,不光是单片机程序的编写,还有电路的设计。有些公司可能会把单片机开发分成两块:电路设计、程序设计。然后负责电路设计的人只负责电路设计,不用考虑单片机编程;程序设计的人只管单片机编程,不...

...元件,如果不注意根本感觉不到它的存在,这个元件就是晶振。如果说微处理器是电脑板的核心,它就是微处理器的心脏。晶振的概念晶振是晶体振荡器的简称,实际上通常说的晶振也包括晶体谐振器,因为其核心都是一块石英...

咱搞硬件的,应该都使用过晶振,上次写开关电源环路的零极点的时候,忽然想到晶振是自己起振的,如果从环路的角度看,应该就是利用的环路不稳定的特性,产生自激振荡。除此之外,我又想到下面这些问题:那么我们使用...

...如果需要对这两种音频同时支持的话,声卡就需要有两颗晶振。但是娱乐级声卡为了降低成本,通常都采用SRC将输出的采样频率固定在48kHz,但是SRC会对音质带来损害,而且现在的娱乐级声卡都没有很好地解

...如果需要对这两种音频同时支持的话,声卡就需要有两颗晶振。但是娱乐级声卡为了降低成本,通常都采用SRC将输出的采样频率固定在48kHz,但是SRC会对音质带来损害,而且现在的娱乐级声卡都没有很好地解

1、单片机晶振不起振原因分析遇到单片机晶振不起振是常见现象,那么引起晶振不起振的原因有哪些呢?(1)PCB板布线错误;(2)单片机质量有问题;(3)晶振质量有问题;(4)负载电容或匹配电容与晶振不匹配或者电容质量有问题;(5...

什么是晶振晶振一般叫做晶体谐振器,是一种机电器件,是用电损耗很小的石英晶体经精密切割磨削并镀上电极焊上引线做成。对于单片机来说晶振是很重要的,可以说是没有晶振就没有时钟周期,没有时钟周期就无法执行程序...

一.晶振电路晶体谐振器是一个无源元件,因此受到电源电压、环境温度、电路结构、电路常数和衬底布线方式等方面的影响,大致可分为正常和异常两种工作方式。因此,在振荡电路的设计中,首先要考虑保证晶体谐振器的振...