晶片镀膜机(国内自主研发一款商用的手机芯片需要多少钱?)

Posted

篇首语:我会努力奋斗直到亮瞎你们的双眼。本文由小常识网(cha138.com)小编为大家整理,主要介绍了晶片镀膜机(国内自主研发一款商用的手机芯片需要多少钱?)相关的知识,希望对你有一定的参考价值。

晶片镀膜机(国内自主研发一款商用的手机芯片需要多少钱?)

9月1日,联发科(MediaTek)曝光了其首款集成5G调制解调器的7nm SoC,采用ARM Cortex-A77 CPU 核心、以及 Mali-G77 GPU。

据了解,MTK 首颗 5G SoC 采用了台积电的 7nm 制程,集成了联发科自家的 Helio M70 调制解调器。

这款基带支持 6GHz 以下的 5G NR 频谱、高达 2x 的载波聚合、以及独立 / 非独立的 5G 网络架构。全球首款采用先进7nm工艺的5G 芯片,在极小的封装中实现大幅节能。高速吞吐:峰值吞吐量达到4.7Gps下载速度(Sub-6GHz频段),支持新空口(NR)二分量载波(CC),支持非独立(NSA)与独立(SA)5G组网架构。强大的多媒体与影像性能:支持60fps的4K视频编码/解码,以及超高分辨率摄像机(80MP)。

那么研发一款类似的芯片需要多少钱?

芯片代工行业在制程迈入10nm以内后,面临的成本压力也越来越高。据SemiEngineering报道,IBS的测算显示,10nm芯片的开发成本已经超过了1.7亿美元,7nm接近3亿美元,5nm超过5亿美元。如果要基于3nm开发出NVIDIA GPU那样复杂的芯片,设计成本就将高达15亿美元。而上面所提到的联发科开发的是一款既有ARM CPU又有基带处理部分的SoC芯片,上面用到了众多的IP核和复杂的异构工艺部分,甚至比NVIDIA GPU还要复杂。我们试着分析一下成本。

1、流片费用:7nm FinFET工艺流片费用约3000万美金(参考下面麒麟990流片费用,同时兼顾考虑联发科与台积电同属台湾地区,可能有优惠),合2亿人民币;根据业内人士@手机晶片达人在微博上的爆料称,麒麟990处理器目前正在用台积电7nm Plus EUV的工艺设计中,预计将在明年第一季流片。同时这位业内人士还表示,此次麒麟990处理器仅流片费用就高达3000万美金,足以表明华为的决心。

上面提到的FinFET工艺,其实就是华人科学家胡正明教授发明的(胡正明教授还提出了著名的BSIM模型)。也是为了解决芯片做到更小尺寸的一种方法,据说16nm FinFET工艺的价格,不管芯片的面积有多大,起步价500万美金。

2、IP授权购买费:主要是购买了ARM最新的Cortex-A77CPU、Mali-G77GPU授权,估计其他一些小的模块应该也有购买的,如音视频编解码器什么的。按生命周期5000万颗算,各种ip授权购买费按每颗40元算,这大概20亿。单ARM CPU授权一项,据悉,每次约1亿美金。

3、自研部件费用:联发科这款5G SoC 集成了自研的最先进的独立AI处理单元APU完全保证用户对于5G网络环境下手机的使用需求。除比较复杂的APU外,自研部件还包括多模通讯基带(2G3G4G5G等),相机isp,各种控制开关,微核等。这部分很难估算,而且是长期的研发的成果。这部分成本暂复算为10亿人民币。

4、高通专利费:按5000万颗算,每颗交10元,合5亿人民币。

5、研发工程师工资奖金。1000名工程师每年按50万计算,3年合计15亿。

以上各项共计2+20+10+5+15=52亿人民币。而这些还不包括架构开发,生态构建等的费用。

也许大家觉得这种复杂的SoC芯片比较特殊,需要花费的成本价当然比较高。那么咱们可以看一下一款普通的NAND FLASH控制器芯片需要多少钱才能开发出来?

研发一款商用的普通NAND FLASH接口控制器芯片需要多少钱?

大家知道,NAND FLASH控制器芯片其实功能很单一,仅仅只是通过PCIe接口按照NVMe之类的协议来把指令交给FLASH芯片,同时把数据在HOST主机和FLASH芯片及DDR上搬来搬去而已。

下图来自于实际商用NAND FLASH产品宣传时的PPT,从图中可以看出,开发一颗NAND FLASH主控芯片前期投入(软件、硬件、IP及人力和时间费用,软件工具费,设计服务费及仪器测试费用等)的开发费用折合人民币约为1.35亿人民币,而后期流片、封测等费用为2200万元人民币,共计约1.57亿人民币。

2018年,NAND Flash正式进入3D制程发展,其相关控制芯片之晶圆制造制程则在近两年正式进入1x纳米时代,因此NAND Flash控制芯片的设计愈加复杂、所需要运用的人力及资金等资源耗费较市场成长的幅度高,以目前全球PCIe规格效能跑分评鉴最佳的群联电子SSD控制芯片PS5012-E12来看,该颗芯片的成功除了累积数十年的功力外,在研发人力、时间、设计工具、晶圆先进制程光罩费、3D NAND验证费…等等资源全数换算为可被评价的费用,总计超过1.55亿人民币。

有同学可能说,如果做更简单的芯片呢?没有上面所说的购买IP、人力成本、甚至软件成本都不考虑,自己写RTL代码,自己做后端版图,那么剩下的最大的成本恐怕就剩下流片了。当然,这种情况在高校和一些研究机构可能存在。软件工具如果按照市场价格从仿真、综合到后端布局布线,每一步骤都有相应的软件,而这些软件LICENSE的使用费用(主要是Cadence和Synopsys等之类的工具),每一种半年的LICENSE使用费用都在100万人民币以上(只是一个key的价格,多个人还需要买多个)。

所以,从上面的两个例子来看,华为海思十年间在芯片上投入的资金就达到3940个亿,这个近4000亿的投资多吗?

不多。

流片费用是成本里较大的组成部分

工艺进入28nm后,芯片的流片成本成指数级增长。“如果说2014年开一个28nm的芯片200-300万美元对很多公司来说已是不堪重负,那么,未来,开一款16nm的芯片成本将在千万美元左右,而开一款10nm的芯片,从现在各项投入来看,可能需要达到1.3亿美元。”在“2014上海FD- SOI论坛”上,芯原微电子公司技术市场和应用工程师资深总监汪洋说道。不过,尽管如此昂贵,他透露国内仍有一些真土豪提出要开16nm的芯片,主要是那些为挖金币而定制的处理器芯片。

几年前,采用不太先进的16nm工艺,流片费用需要1500万美金以上。

如果是这两年,采用7nm的工艺,流片费用需要准备1-3亿美金以上。

而十年前,海思给出的平均每颗商用芯片的研发成本仅为4000万人民币。

这里面有太多太多的原因。要研制出一块芯片很容易,但是要在控制温度、成本以及功耗的情况下实现量产,却不是一件容易的事,换句话来说,就是芯片制造一共有两个难点,首先就是在试验阶段投入的资金非常的高昂,一次大概需要10万块钱,从设计到加工的过程中走过的工序差不多就有3000到5000道,而且一次耗费的时间差不多就是一年,在时间和金钱的制约下,对于其精度的要求是极其的高。其次就是排错难度大,虽然芯片看上去的体积非常小,但是在上面却分布着数亿个晶体管,可以被检测出来的信号最多也就只有几百条,能够看到如果哪条晶体管出了差错,那都是难上加难!除了这些技术方面的原因之外,还有国际因素,因为有专利权和出口协定的管控,因此我们想从一些拥有芯片技术的老牌国家中获取先进的技术根本是不可能的事情,而且中国每年进口一台相关的仪器,其中的专利费就高得吓人,像前段时间买入中国的阿斯麦光刻机,一台价值就要8亿元!

当然,如果想办法,做芯片还是有不少省钱的办法的。不用买IP,在高校里面找廉价的学生来设计(没有研发成本),租用高校里面的EDA工具,自己从RTL代码一直坐到GDSII,再采用便宜的MPW,选择非常古老的工艺线,不用量产,仅做做实验,那么计算下来一颗芯片流片一次的费用也至少需要几十万元人民币。如果是项目要用的稍微复杂一点的芯片,那么一次流片至少也需要几百万人民币。如果一次流片后还有BUG,再流片的话还得花费五六百万,如此反复的烧钱。

可做芯片成本这么高,听说有的地方的学生学一门课,然后全班的学生都可以自己做出来一颗芯片来交作业?

高校里上一门课然后布置所有学生都做出一颗芯片的作业现实中存在吗?

是存在的。

有人曾经看到过台湾的大学芯片专业的学生全班同学都可以流片,好像觉得流片跟做个PCB板子差不多一样,其实不是这样的。台湾有个组织叫CIC(国研院晶片中心),只针对台湾的业界、学术界有优惠,CIC设立的初衷就是为台湾的IC产业提供良好的服务和保障,TSMC 28nm工艺的,小面积下大约是23.5万人民币每平方毫米;45nm大约是12万人民币每平方毫米(CIC公开报价)。其实毫米非常小,做芯片随随便便就有N个平方毫米。前面所说的全班都可以流片的就是TSMC的180nm工艺线(教育线),比如平时大学本科的模电课,一学期上完了,全班都可以申请流片做个放大器什么的,毕业设计就更不用说了。这个教育线在台湾地区几乎是免费的。所以,几乎可以人人做芯片,这也是为什么台湾地区的芯片设计和制造比较厉害的关键原因。

这种把流片当做跟吃饭一样随便的地方澳门也有。

比如,IEEE fellow,IET fellow、中国科学院海外特聘专家,现任澳门大学教授、微电子研究院副院长、模拟与混合信号超大规模集成电路国家重点实验室副主任麦沛然教授课题组。

3年21篇ISSCC顶级会议论文,凭什么?

除了自身实力之外,凭的就是不断的流片实验的经验积累。培养几届学生专盯某一个具体的点,工作具有良好的延续性。精心设计,用先进工艺,测试结果的优势就出来了。而且,芯片小,一个学生就可以负责一颗,一方面可以用心打磨,另一方面可以快速出多篇优化方案。选择小点突破,为工程准备预案。如果咱们也有这样的环境和条件,流片如吃饭般容易,是否也可以做成这种效果?仔细想想,似乎不难,就针对某种电路往死里优化,先仿真出来,再去流片验证,是不是也不难啊?电路结构千千万,即便是数字的,如果有这种烧钱的条件,肯定会有一两个点会突破的。难就难在流片费用太高,资金不足。

说实话,大陆高校里面每年能有一两次流片机会的高校都屈指可数,更别提如上面的例子中根据需要尽情的流片的高校是完全不存在。当然,国内还是有不少渠道能够减免一些流片费用的,比如去年中兴事件后,各地政府部门出台的一些扶植芯片的政策,有的地方甚至可以申请免费流片(其实费用是政府部门出了)。

希望今后大陆的集成电路制造业也能够飞速发展,至少让教育界的老师和学生们能够实现“流片自由”。

附录:芯片是一层一层长出来的

CPU芯片的成本构成是这个样子滴

1、晶片成本

要制造CPU,第一步是制造晶圆(将晶圆切成小片后即可得到晶片)。晶圆的成分是硅,是地壳内第二丰富的元素(沙子的主要成分就是二氧化硅)。制取晶圆分为三个步骤:

一是制取电子级硅。通过碳和二氧化硅在电弧熔炉中反应得到冶金级硅,再对其进一步提纯,将粉碎的冶金级硅与气态的氯化氢进行氯化反应,生成液态的硅烷,通过蒸馏和化学还原工艺,得到电子级硅,其纯度高达99.999999%。

二是制取硅锭。将电子级硅放在石英坩埚中,并用石墨包围不断加热,温度维持在大约1400℃,炉中充斥着惰性气体,使电子级硅熔化的同时,不会因化学反应而掺杂杂质。

随后将一颗籽晶浸入坩埚中,由拉制棒带着籽晶与坩埚旋转方向逆向旋转,采用旋转拉伸法缓慢将籽晶垂直拉出,熔化的多晶硅会粘在籽晶的底端,最终得到圆柱体的硅锭。

三是切割圆晶。将得到的硅锭横向切割成圆形的单个硅片,然后进行研磨,将凹凸的切痕磨掉,再用化学机械抛光工艺使其至少一面光滑如镜。

目前,国际主流采用的是12英寸晶圆。就国内而言,中芯国际和华力微都有12英寸晶圆厂,英特尔、三星、海力士等公司在大陆也有12英寸晶圆厂。

虽然12英寸晶圆厂的投资远远大于8英寸晶圆厂,但是晶圆尺寸越大,意味着单片晶圆能够切割出的芯片越多,芯片成本也就越低。

在设备成本被以亿为单位的芯片出货量平摊后,采用尺寸更大的晶圆,不仅芯片价格可以更具竞争力,还能以细水长流的方式获取更多利润。

因此,晶片成本就是以二氧化硅制取晶圆所耗费的资金分摊到每一片晶片后的成本,可以简单理解为每一片芯片所用的材料(硅片)的成本。

2、掩膜成本

在得到晶圆后,要制造CPU,还要进行以下步骤:

一是湿洗。用各种化学药剂清洗晶圆,确保晶圆表面没有杂质。

二是光刻。使用光刻机将激光光束穿透画着线路图的掩膜,经物镜补偿各种光学误差,将电路图成比例缩小后映射到硅片上,然后使用化学方法显影,得到刻在硅晶片上的电路图。

光刻示意图。最上方的是掩膜,中间的是物镜,用来补偿各种光学误差,最后将电路图成比例缩小后映射到硅片上。

三是离子注入。在硅晶片不同的位置嵌入不同的物质,进而形成场效应管(晶体管)。

四是蚀刻。使用刻蚀机将晶片上多余的部分去掉,得到所想要的结构。

五是等离子冲洗。用较弱的等离子束轰击整个芯片,达到清洁的效果。

六是热处理。瞬间把晶圆加热到1200摄氏度以上,然后慢慢地冷却下来,使得注入的离子能更好地被启动以及热氧化,并在晶片中形成场效应管的栅极。

七是气相淀积。通过物理、化学气相淀积设备进一步精细处理晶片表面,并给晶片镀膜。

八是电镀、化学、机械表面处理。

因此,掩膜成本就是晶片加工成本以及光刻机、刻蚀机、物理、化学气相淀积设备的折旧成本等等。掩膜成本的高低和制程工艺的关系非常大,像40/28nm的工艺已经非常成熟,成本也低,40nm低功耗工艺的掩膜成本为200余万美元;28nm SOI工艺为400万多美元;28nm HKMG成本为600多万美元。

但在最新的制程工艺问世之初,耗费则颇为不菲。在2014年刚出现14nm制程时,曾有消息称其掩膜成本为3亿美元。

当然,随着时间的推移和台积电、三星掌握14/16nm制程,现在的价格应该不会这么贵。英特尔正在研发的10nm制程,根据英特尔官方估算,掩膜成本至少需要10亿美元。

新制程工艺之所以贵,一方面是贵在新工艺高昂的研发成本和偏低的成品率,另一方面也是因为光刻机、刻蚀机等设备的价格异常昂贵。

以前道光刻机为例,国内商业化量产依旧停滞在90nm,40/65nm的光刻机虽然取得技术突破,但依旧没有商业化量产,有可能还处于实验室状态。

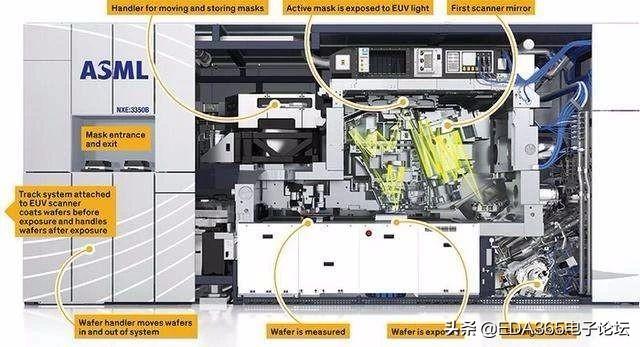

中芯国际、华力微等晶圆厂的28nm光刻机完全依赖进口,而且价格颇为不菲——ASML主流技术水平的光刻机售价为几千万美元,最先进的EUV光刻机问世时售价曾高达1亿美元……

光刻机

每片CPU的掩膜成本=掩膜总成本/总产量,因此,如果产量小,CPU的成本会因为掩膜成本而较高,只要产量足够大,比如每年出货以亿计,掩膜成本被巨大的产量分摊到微乎其微。

3、封测成本

晶圆倒装机

在晶片完成上述光刻、刻蚀等步骤后,还需要用后道光刻机、减薄机、划片机、装片机、引线键合机、倒装机等制造设备给晶片装个壳,将之前加工好的晶片和基片、散热片堆叠在一起,最终形成我们日常见到的四四方方、带针脚和商标的CPU。

封装成本就是这个过程所需要的资金。在产量巨大的一般情况下,封装成本一般占硬件成本的5%-25%左右,不过IBM的有些芯片封装成本占总成本一半左右,据说最高曾达到过70%......

测试可以鉴别出每一颗处理器的关键特性,比如最高频率、功耗、发热量等,并决定处理器的等级,比如将一堆芯片分门别类为:i54460、i54590、i54690、i54690K等,之后英特尔就可以根据不同的等级,开出不同的售价。如果芯片产量足够大的话,测试成本在CPU总成本的占比可以忽略不计。

以已经非常成熟的40nm低功耗工艺为例,采用该制程工艺的CPU,其测试成本约为2美元,封装成本约为6美元。

4、设计成本

设计成本主要包括专利成本、开发工具成本、工程师工资和场地费用等。

一是专利成本。目前,国内只有像龙芯、申威等少数走独立自主技术路线的IC设计公司可以做到自己设计的CPU/微结构不含第三方IP,比如申威411、申威1621,龙芯3A2000/3B2000/3A3000/3B3000,以及微结构GS464E皆不含第三方IP。而国内其他IC设计公司基本上还处于购买国外IP做集成的阶段,主要的IP供应商都是国外公司。

以海思、展讯、联芯、全志、瑞芯微、新岸线等ARM阵营IC设计公司为例,这些公司无一例外依赖于ARM的IP授权——海思的麒麟950就购买了ARM Cortex A53和A72,不仅要一次性支付一笔不菲的授权费,而且每生产一片芯片,还要支付一定的专利费……

这种购买IP授权的商业模式,实际效果是ARM犹如开启了印钞机,而国内IC设计公司只能赚一点辛苦钱,直接导致国内ARM阵营IC设计公司“操的是卖白粉的心,赚的是卖白菜的钱”。

二是开发工具成本。要设计CPU就离不开EDA(电子设计自动化)工具的辅助,比如前端设计的仿真环境,低功耗流程设计工具,时序仿真工具,芯片后端设计的工具等等。

要购买这些EDA工具,同样耗费颇为不菲,特别是国内IC设计公司的EDA工具大多数都依赖于国外公司的情况下(国内研发EDA工具做的最好的是华大九天,但市场份额比较小)。

三是工程师的工资等成本。像IBM、AMD、Marvell等IC设计公司中,有5年以上经验的工程师的月薪在25K-50K之 间,国内海思、展讯、联芯有5年以上经验的工程师的月薪也在15K-30K之间。

假设一个IC设计公司有500人(英特尔公司有约10万员工),每个员工以月薪20K计算,光工资成本一年就需要1.2亿元……

四是其他成本。比如公司场地租用、宣传营销、行政开销等零零碎碎的成本开销,这些开销因各个公司的情况有所不同,而且有的差距会非常大。

国产CPU售价为何居高不下

为了形象地解释这个问题,我们假设两款国产CPU:CPU-X和CPU-Y。

首先看晶片成本。

假设CPU-X采用40nm制程,芯片面积200平方毫米;CPU-Y采用28nm制程,芯片面积140平方毫米(制程越小,晶片面积越小)。

一片12寸晶圆价格为4000美元,面积约为7万平方毫米。经计算可以得出,一片12寸晶圆可以切割出299个CPU-X或495个CPU-Y(40/28nm技术已经非常成熟,切割成本差异非常小,就忽略不计了)。

由于在将晶圆加工、切割成晶片的时候,并不能保证100%成果,因而存在一个成品率的问题,以49%的成品率计算,一片12寸晶圆可以切出146个符合良品标准CPU-X或242个CPU-Y,最后12寸晶圆的价格/切割出的成品晶片,可以得出结论:

采用40nm制程的CPU-X的晶片成本为27.3美元;

采用28nm制程的CPU-Y的晶片成本为16.5美元。

可以看出,采用更先进的制程,能够有效降低晶片成本。

其次看掩膜成本。

上文已经提到过40/28nm的工艺已经非常成熟,40nm低功耗工艺的掩膜成本约为200万多美元。

如果CPU-X的产量为10万片,则分摊到每一片CPU上的成本为20美元;

如果CPU-X的产量为100万片,则分摊到每一片CPU上的成本为2美元;

如果CPU-X的产量为1000万片,则分摊到每一片CPU上的成本为0.2美元;

28nm HKMG掩膜成本为600多万美元,

如果CPU-Y的产量为10万片,则分摊到每一片CPU上的成本为60美元;

如果CPU-Y的产量为100万片,则分摊到每一片CPU上的成本为6美元;

如果CPU-Y的产量为1000万片,则分摊到每一片CPU上的成本为0.6美元。

由此可见,在使用相同工艺的情况下,随着CPU的产量增加,CPU的掩膜成本会逐步降低,如果产量以亿为单位,即便使用最昂贵的14/16nm制程工艺,其掩膜成本也可以被压缩到3美元以内。

再次看封测成本。

封装成本一般占硬件成本的5%-25%左右,之前讲过,比如CPU-X采用非常成熟的40nm制程,其测试成本约为2美元,封装成本约为6美元。

最后看设计成本和其他成本。

设计成本非常不好量化,因为各家IC设计公司员工数量不同,购买IP的耗费、购买EDA工具的成本各异。其他成本同样不好量化,各家公司场地租用、宣传营销、行政开销等所耗费的资金差距非常大。

由于设计成本和其他成本非常不好量化,笔者按国际通用的低盈利芯片设计公司的定价策略8:20定价法来计算最后的售价,也就是硬件成本为8的情况下,定价为20(在不购买国外IP的情况下,一般能做到这个定价)。

别觉得这个定价高,其实已经比较低了,英特尔一般定价策略为8:35,AMD历史上曾达到过8:50……

CPU硬件成本包括晶片成本+掩膜成本+测试成本+封装成本四部分。

如果CPU-X的产量达到10万片,则掩膜成本为20美元,加上27.3美元的晶片成本和8美元的封测成本,其硬件成本为55.3美元,采用8:20定价法,其售价为138.25美元。

如果将CPU-X的产量达到100万片,其硬件成本为37.3美元,采用8:20定价法,其售价为93.25。

如果CPU-Y的产量为10万片,则掩膜成本为60美元,之前计算过晶片成本为16.5美元,加上封测成本,那么硬件成本为85美元左右,采用8:20定价法,其售价为212.5美元。

如果CPU-Y的产量为100万片,则掩膜成本为6美元,硬件成本约为30美元,其售价约为75美元。

显而易见,虽然使用更先进的制程会导致掩膜总成本提升,但却可以降低晶片成本。

而只要产量足够大,就可以使每片CPU的掩膜成本大幅降低,使拥有“更贵的制程工艺+更大的产量”属性的CPU,会比拥有“便宜的制程工艺+较小的产量”属性的CPU的成本更低,特别是在产量相差100倍的情况下,成本上的差距会犹如鸿沟。

那国产CPU的产量为何上不去呢?

像龙芯、申威等自主CPU,由于另起炉灶,自建技术体系,必然和现有的Wintel(微软+英特尔)体系不兼容,在PC市场被Wintel垄断的情况下,自然导致市场化进程步履维艰。

而兆芯虽然同样采用X86指令集,可以跑Windows,不存在软件生态问题,但在技术上完全依赖于威盛公司,自然提高了成本,加上性能孱弱,不具备市场竞争力——即便一味扩大产能,也只能是产量越大,亏得越多,所以只能在党政军市场寻求机会,产量自然非常有限。

总之,抛开国内IC设计公司和英特尔在设计能力的差距不谈,单纯讲制程工艺和产量对性能和成本的影响,在国产CPU产量非常小的情况下,即便使用非常便宜的制程工艺流片,依旧导致其成本比英特尔的CPU要高,价格也更贵。

而英特尔则可以依靠市场的垄断地位,即便使用了最贵的制程工艺,以庞大的产量压低成本,攫取超额利润,使自己的利润率高达60%。

相关参考

手机防水纳米镀膜机真的假的(纳米手机防水镀膜靠不靠谱,电视报道后才知道有多坑)

...技术也与手机发生了交集,近日,央视也报道了手机防水镀膜的实验,很多人认为手机防水镀膜非常的不可思议,一个手机喷涂上防水镀膜液就可以成为防水镀膜,其实防水镀膜的

手机纳米镀膜机真的假的(膜结手机纳米防护讲三无和品牌产品的故事手机砸核桃真相)

当下流行的一种叫手机防砸镀膜横空出世了,防砸,防摔。什么铁锤砸,砸核桃,改锥砸,都仿佛金钟罩加身,无论怎么搞都不会坏。这真是一种“神奇”的科技啊。那他到底是什么呢?真能有这样的效果吗?到底是不是真的?...

一部手机里有多少个芯片?处理器、存储、基带、图像处理、电源管理、屏幕显示……它们定义了你手机的几乎一切特性,这些年令国产安卓手机消费者受益颇多的快速充电,很大程度上就要归功于电源管理芯片创新应用。需要...

一部手机里有多少个芯片?处理器、存储、基带、图像处理、电源管理、屏幕显示……它们定义了你手机的几乎一切特性,这些年令国产安卓手机消费者受益颇多的快速充电,很大程度上就要归功于电源管理芯片创新应用。需要...

手机镀膜和钢化膜哪个好(手机防水镀膜是什么膜结手机纳米防护和防水镀膜的区别)

现在很多网上宣传的沸沸扬扬的手机纳米防水镀膜机可以做到让手机起到防水的效果,据我了解有的都是不良商家虚假夸大产品,达到骗钱的目的!防水镀膜本身是有很高技术含量的东西,不是拿一个小小的镀膜机,随便抽抽真...

...加谈判筹码。”那么,我国实现芯片自主可控难在哪里?国内芯片产业发展这么多年,需要注意哪些问题?芯片自主可控难在哪里?中

...加谈判筹码。”那么,我国实现芯片自主可控难在哪里?国内芯片产业发展这么多年,需要注意哪些问题?芯片自主可控难在哪里?中

真空镀膜技术是一种新颖的材料合成与加工的新技术,是为客户的产品做“美容”---外观更丰富多彩、更亮丽。真空镀膜设备是镀膜工业上的一个重要部分。随着全球制造业高速发展,真空镀膜技术应用越来越广泛,当前已被应...

探针仪(用于量子芯片的光刻机、刻蚀机,EDA,我们都研发成功了)

众所周知,目前的硅基芯片已经快要发展到极限了,台积电、三星目前已经实现了3nm的量产,而科学家们预测硅基芯片的物理极限是1nm。而从3nm到1nm之间,也就只有2nm这么一代工艺了,之后就再难前进了。那么在硅基芯片之后,...

淮安德国莱宝真空镀膜机(镀膜设备厂商汇成真空成功IPO,询问如何苹果向印度越南转移产能)

...计募集资金2.35亿元,主要用于研发生产基地项目、真空镀膜研发中心项目和补充流动资金项目。汇成真空的主要业务为真空镀膜设备研发、生产、销售及其技术服务,面向消费电子行业的金属、塑料中框镀膜、ITO导电薄膜镀膜...